## CS1253 芯片用户手册

带 24bits ADC 和 BIM 的高性能 AFE

REV1.0

通讯地址：深圳市南山区蛇口南海大道 1079 号花园城数码大厦 A 座 9 楼

邮政编码：518067

公司电话：+(86 755) 86169257

传 真：+(86 755) 86169057

公司网站：[www\(chipsea.com](http://www(chipsea.com)

# CS1253 芯片用户手册

## 版本历史

|     | 修改记录          | 日期         |

|-----|---------------|------------|

| 1.0 | 更新 WLCSP16 封装 | 2021/08/17 |

# 目 录

|                                 |    |

|---------------------------------|----|

| 版本历史.....                       | 2  |

| 目 录.....                        | 3  |

| 图目录.....                        | 5  |

| 表目录.....                        | 5  |

| 1 简介.....                       | 6  |

| 1.1 主要特性.....                   | 6  |

| 1.2 应用场合.....                   | 6  |

| 1.3 功能说明.....                   | 6  |

| 1.4 极限值.....                    | 8  |

| 1.5 电气特性.....                   | 9  |

| 1.6 可靠性指标.....                  | 9  |

| 1.7 产品型号及引脚.....                | 10 |

| 1.8 典型应用电路.....                 | 11 |

| 2 功能寄存器说明.....                  | 11 |

| 2.1 功能寄存器列表.....                | 11 |

| 2.2 功能寄存器说明.....                | 12 |

| 2.2.1 SYS—系统配置寄存器.....          | 12 |

| 2.2.2 ADC0—ADC 配置寄存器.....       | 12 |

| 2.2.3 ADC1—ADC 配置寄存器 1.....     | 13 |

| 2.2.4 ADC3—ADC 配置寄存器 3.....     | 13 |

| 2.2.5 ADC4—ADC 配置寄存器 4.....     | 14 |

| 2.2.6 ADC5—ADC 配置寄存器 5.....     | 14 |

| 2.2.7 BIM0—BIM 配置寄存器 0.....     | 15 |

| 2.2.8 BIM1—BIM 配置寄存器.....       | 15 |

| 2.2.9 ADO—ADC 转换数据寄存器.....      | 16 |

| 2.2.10 ADS—ADC 转换数据读取标准寄存器..... | 16 |

| 3 功能描述.....                     | 16 |

| 3.1 输入选择.....                   | 16 |

| 3.2 PGA 和 ADC.....              | 17 |

| 3.3 数字滤波器.....                  | 18 |

| 3.3.1 频率响应.....                 | 18 |

| 3.3.2 建立时间.....                 | 18 |

| 3.4 人体阻抗测量.....                 | 20 |

| 3.4.1 正弦信号发生器.....              | 20 |

| 3.4.2 激励电极及测量电极.....            | 21 |

| 3.4.3 整流.....                   | 21 |

| 3.4.4 阻抗校准.....                 | 22 |

| 3.5 参考电压源.....                  | 23 |

| 3.6 内部时钟源.....                  | 23 |

| 3.7 测量模式及其切换.....               | 23 |

| 3.8 多种工作模式.....                 | 23 |

| 3.9 复位和断电(POR&power down).....  | 24 |

| 4 转换有效位.....                    | 25 |

---

|       |                    |    |

|-------|--------------------|----|

| 5     | 典型特性.....          | 26 |

| 5.1   | LDO/VREF 典型特性..... | 26 |

| 5.2   | 内部时钟典型特性.....      | 26 |

| 5.3   | BIM 典型特性.....      | 27 |

| 6     | 三线串行通讯接口.....      | 31 |

| 6.1.1 | 读时序.....           | 32 |

| 6.1.2 | 写时序.....           | 32 |

| 7     | 封装.....            | 34 |

## 图目录

|                                                          |    |

|----------------------------------------------------------|----|

| 图 1.1 CS1253 原理框图.....                                   | 7  |

| 图 1.2 CS1253 引脚图.....                                    | 10 |

| 图 1.3 CS1253 典型应用电路.....                                 | 11 |

| 图 3.1 模拟输入结构图.....                                       | 17 |

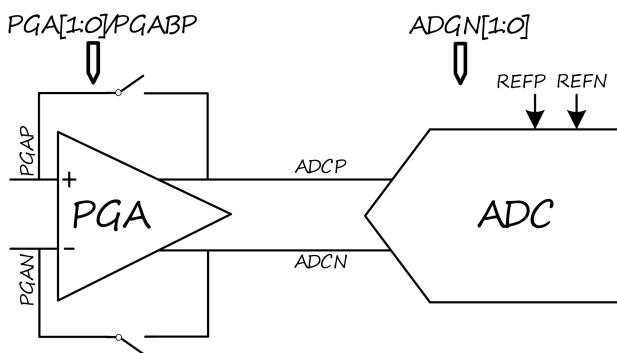

| 图 3.2 PGA 和 ADC 结构图.....                                 | 17 |

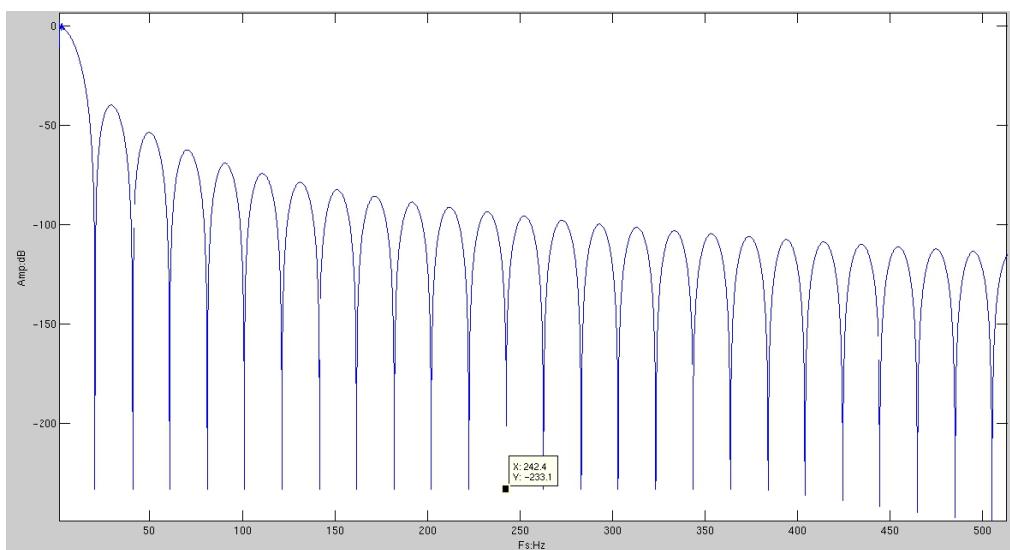

| 图 3.3 COMB 滤波器的频率响应特性(Fs=331Hz, DR=10Hz, 3 阶 COMB) ..... | 18 |

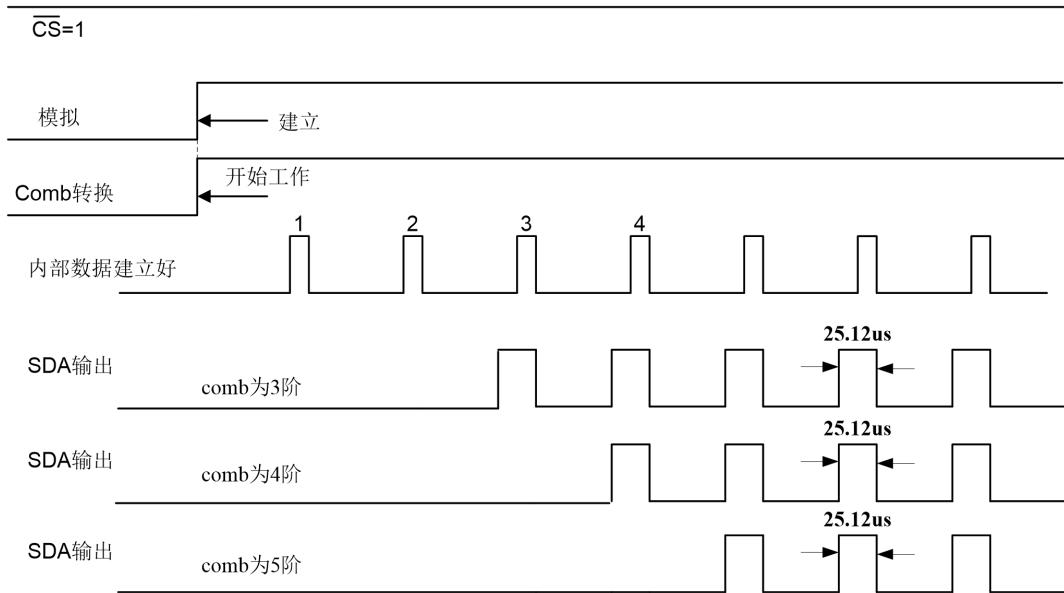

| 图 3.4 COMB 建立过程.....                                     | 19 |

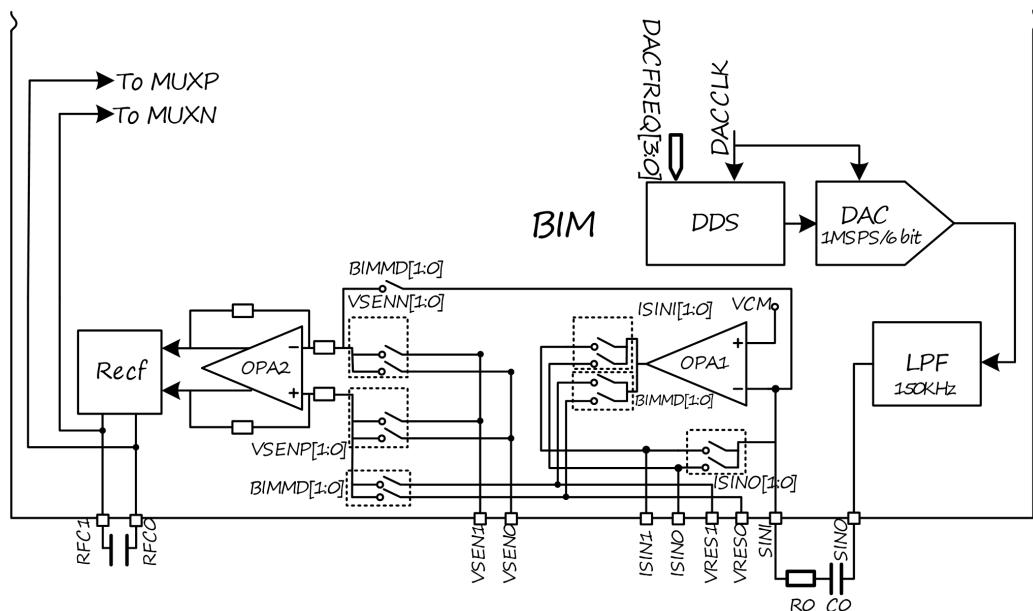

| 图 3.5 BIM 模块结构图.....                                     | 20 |

| 图 3.8 CS1253 低功耗工作示意图.....                               | 24 |

| 图 5.1 内部时钟全电压全温度范围的典型特性.....                             | 26 |

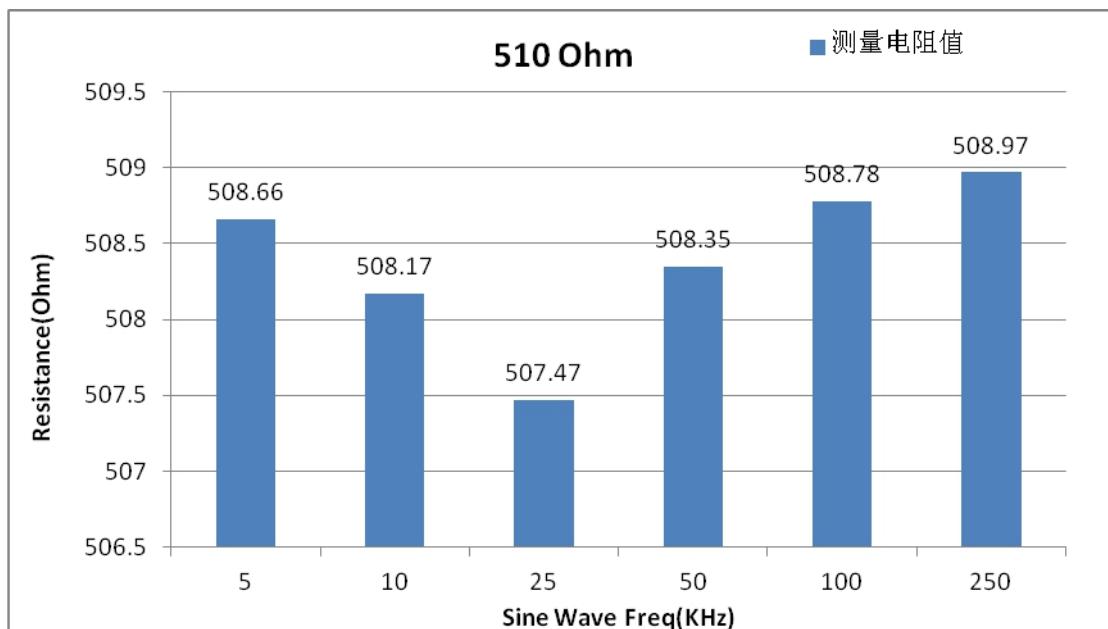

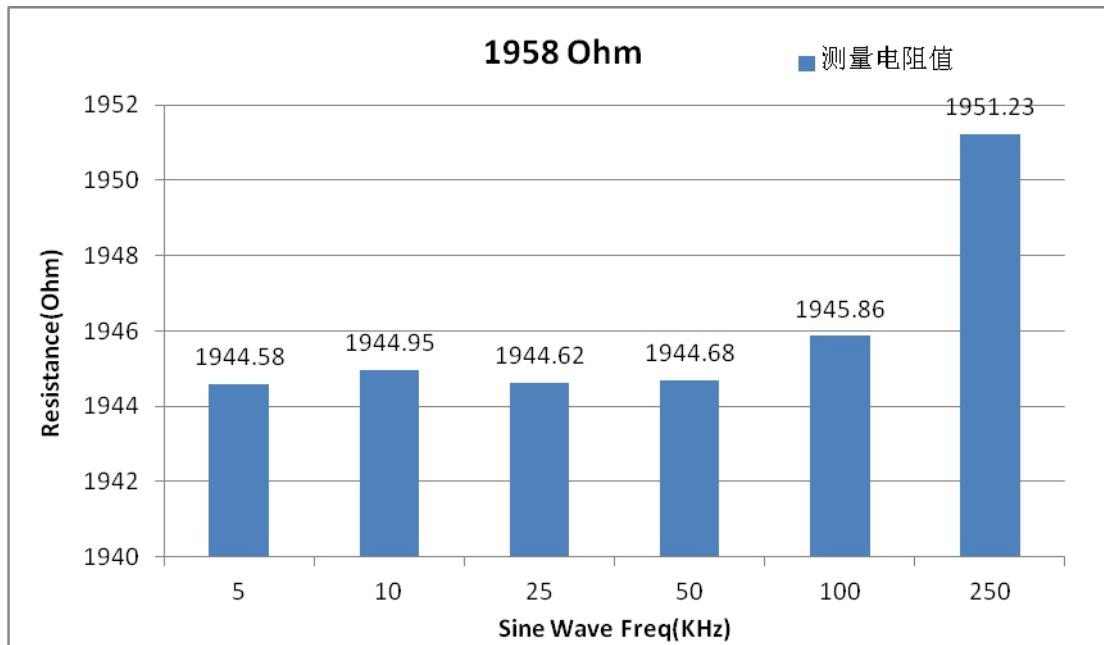

| 图 5.2 FWR 模式下 220 欧姆纯电阻网络的测试结果.....                      | 27 |

| 图 5.3 FWR 模式下 1000 欧姆纯电阻网络的测试结果.....                     | 27 |

| 图 5.4 FWR 模式下 1958 欧姆纯电阻网络的测试结果.....                     | 28 |

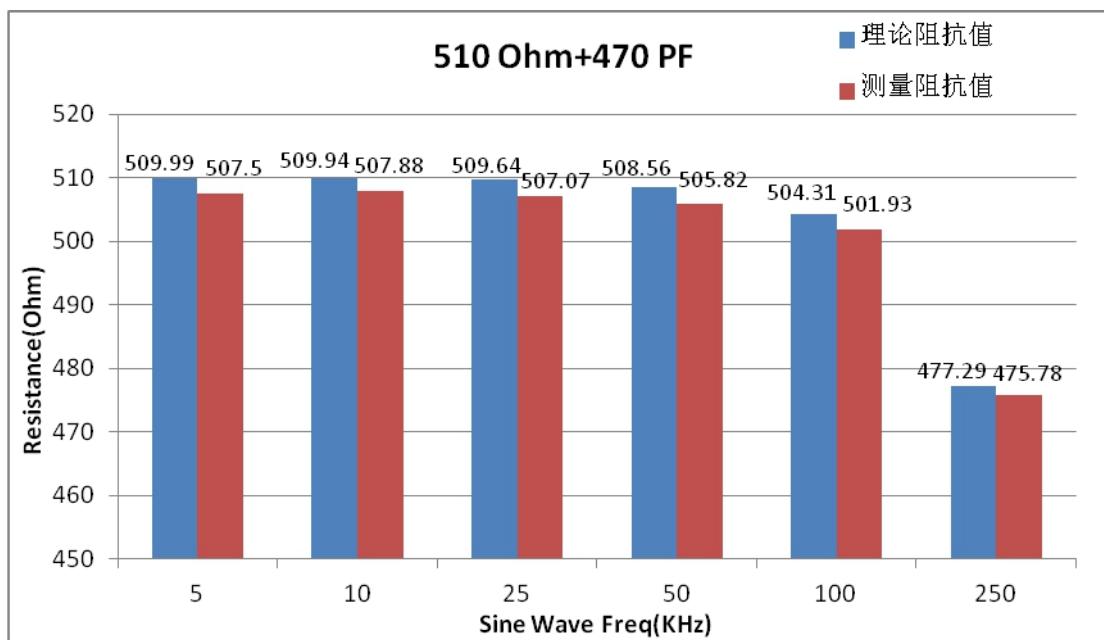

| 图 5.5 FWR+MIX 模式 510ohm+470pF 并联网络的阻抗绝对值测试结果.....        | 28 |

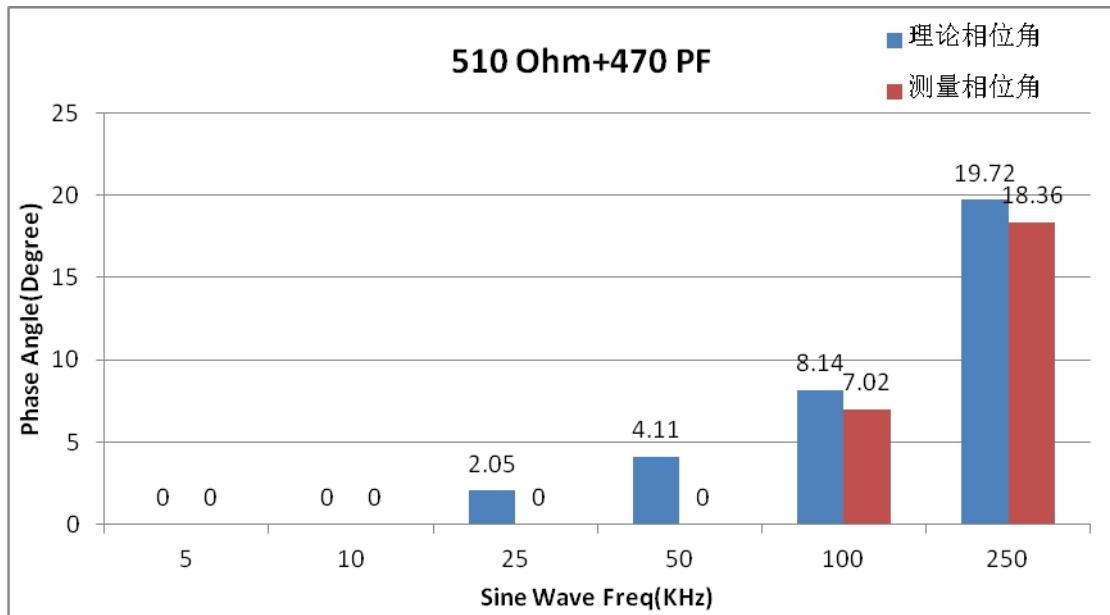

| 图 5.6 FWR+MIX 模式 510ohm+470pF 并联网络的相位角测试结果.....          | 29 |

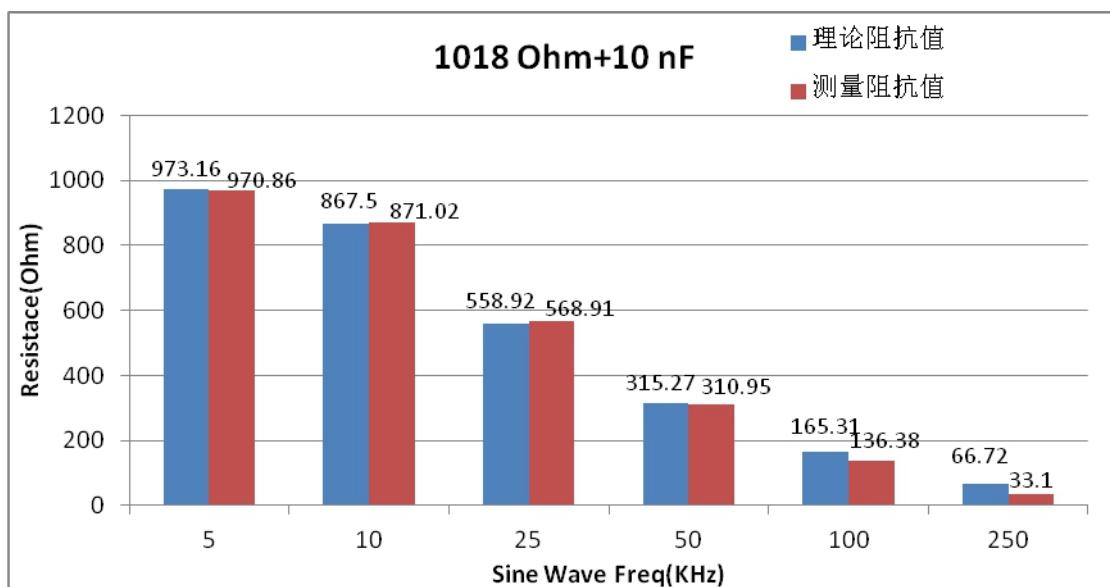

| 图 5.7 FWR+MIX 模式 1018Ohm+10nF 并联网络的阻抗绝对值测试结果.....        | 29 |

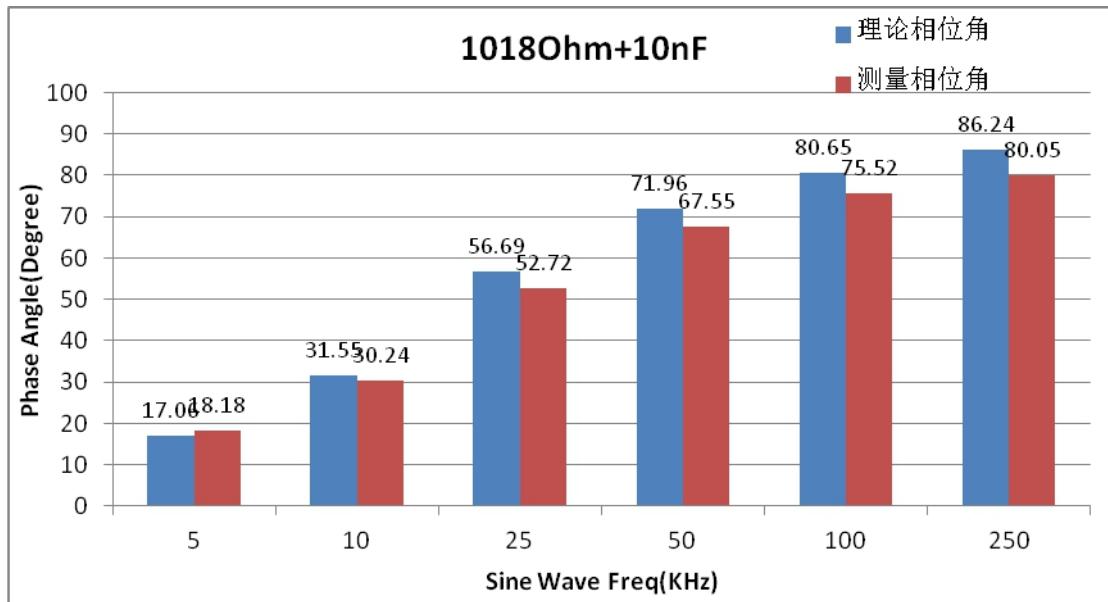

| 图 5.8 FWR+MIX 模式 1018Ohm+10nF 并联网络的相位角测试结果.....          | 30 |

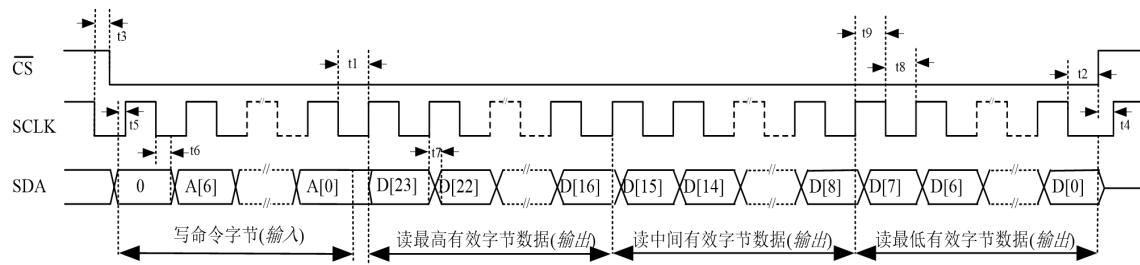

| 图 6.1 读操作时序 1(读 AD 值).....                               | 32 |

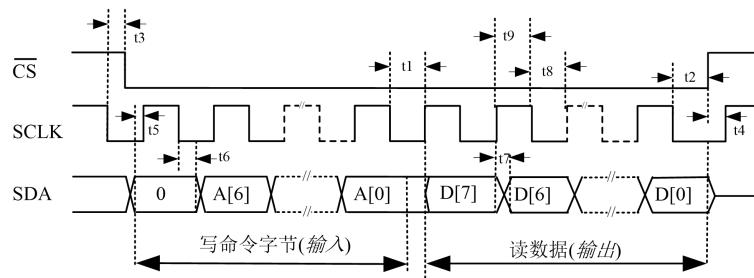

| 图 6.2 读操作时序 2(除 AD 值之外的寄存器).....                         | 32 |

| 图 6.3 写操作时序.....                                         | 33 |

| 图 7.1 芯片 SOP16 封装尺寸信息.....                               | 34 |

## 表目录

|                        |    |

|------------------------|----|

| 表 1.1 CS1253 极限值.....  | 8  |

| 表 1.2 CS1253 电气特性..... | 9  |

| 表 1.3 CS1253 引脚说明..... | 10 |

| 表 2.1 功能寄存器列表.....     | 11 |

| 表 2.2 SYS 寄存器说明.....   | 12 |

| 表 2.3 ADC0 寄存器说明.....  | 12 |

| 表 2.4 ADC1 寄存器说明.....  | 13 |

| 表 2.6 ADC3 寄存器说明.....  | 13 |

| 表 2.7 ADC4 寄存器说明.....  | 14 |

| 表 2.8 ADC5 寄存器说明.....  | 14 |

| 表 2.9 BIM0 寄存器说明.....  | 15 |

| 表 2.10 BIM1 寄存器说明..... | 15 |

| 表 2.11 ADO 寄存器说明.....  | 16 |

| 表 2.12 ADO 寄存器说明.....  | 16 |

| 表 6.1 串口通讯命令列表.....    | 31 |

| 表 6.2 三线串行通讯接口时序表..... | 33 |

# 1 简介

## 1.1 主要特性

### ◆ BIM

- 支持 4 电极测量

- 支持 5K/10K/25K/50K/100K/250KHz 多档频率测量

- 支持阻抗绝对值和相角测量

### ◆ ADC

- 24 bit 分辨率

- 输出速率 10~1280Hz 8 档可选

### ◆ ADC 有效位

- 2.35V 参考、40Hz 速率、128 倍增益下 19.5bits 有效位

### ◆ LDO 及内部参考电压

- 自带 LDO，输出 2.35/2.45/2.8/3.0V 可选

### ◆ 支持性能、普通、低功耗、休眠模式

### ◆ 支持电压测量、BIM 测量及手动测量模式，单命令切换

### ◆ 低漂移片上时钟

### ◆ 三线串行通讯

### ◆ 针对穿戴场景的特点优化了动态范围，适应小电极情况下的高接触阻抗测量

## 1.2 应用场合

人体阻抗分析

交流测脂

手环等便携式设备测脂等

## 1.3 功能说明

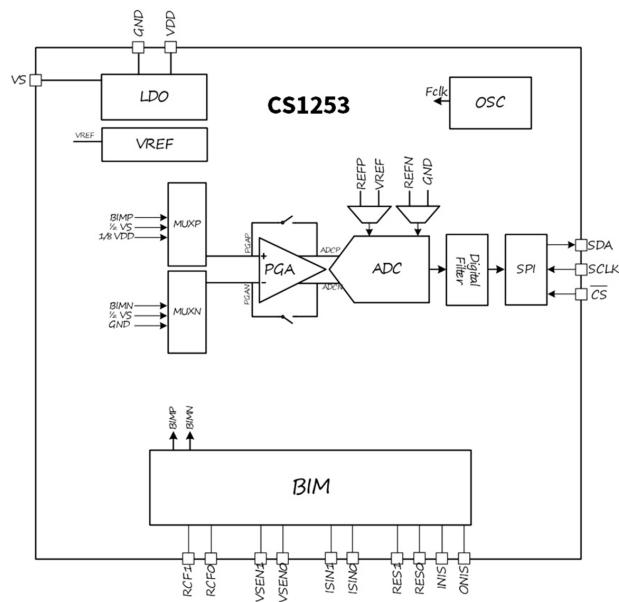

CS1253 原理框图如图 1 所示。

## 图 1.1 CS1253 原理框图

CS1253 是一个包括一个 ADC 信号链和人体阻抗测量模块(BIM)，其中 ADC 信号链包括有输入 MUXP/MUXN，可编程低噪声增益放大器(PGA)，以及一个 Sigma-delta ADC 及数字滤波器 Digital Filter；其中 MUXP/MUXN 具有 3 个内部输入通道；PGA 和 ADC 具有多种增益选择，数字滤波器可配置为多种输出速率。人体阻抗测量模块采用正弦激励源，将人体阻抗转化为电压信号送到 ADC 信号链进行测量，可以支持多电极、多频率人体阻抗测量。

CS1253 内置有低漂移 LDO 和电压基准 VREF，高精度振荡器 OSC 等。

CS1253 可以通过 3 线串行接口进行多种功能模式的配置，例如用作人体阻抗分析、电源电压检测等等。

## 1.4 极限值

表 1.1 示出了CS1253的极限值。

表 1.1 CS1253 极限值

| 名称           | 符号  | 最小   | 最大      | 单位 | 说明                                   |

|--------------|-----|------|---------|----|--------------------------------------|

| 极限电源电压       | VDD | -0.3 | 6       | V  | VDD to GND                           |

| 电源瞬间电流       |     |      | 100     | mA | Input Current<br>momentary           |

| 电源恒定电流       |     |      | 10      | mA | Input Current<br>continuous          |

| 数字管脚输入<br>电压 |     | -0.3 | VDD+0.3 | V  | Digital Output<br>Voltage to GND     |

| 数字输出管脚<br>电压 |     | -0.3 | VDD+0.3 | V  |                                      |

| 节温           |     |      | 150     | °C | Max. Junction<br>Temperature         |

| 工作温度         |     | -40  | 85      | °C | Operating<br>Temperature             |

| 储存温度         |     | -60  | 150     | °C | Storage<br>Temperature               |

| 芯片管脚焊接<br>温度 |     |      | 300     | °C | Lead Temperature<br>(Soldering, 10s) |

## 1.5 电气特性

芯片供电电压为 2.4V-3.6V, 工作温度为-40°C至 85°C, 设计指标如下所示:

表 1.2 CS1253 电气特性

(Test Condition: VDD=3.0V,25°C,VS=2.35V;)

| 参数         | 条件       | 最小值          | 典型值               | 最大值               | 单位     |

|------------|----------|--------------|-------------------|-------------------|--------|

| BIM        | DAC 分辨率  |              | 6                 |                   | bit    |

|            | DAC 速率   |              | 1                 |                   | MSPS   |

|            | 正弦激励波频率  | 5            | 50                | 250               | KHz    |

|            | 正弦激励电流   |              | 375 <sup>1)</sup> |                   | uA     |

|            | 动态范围     | 0            |                   | 2.5*限流电阻          | ohm    |

|            | 线性度      | 0~1*限流电阻     | 0.5               |                   | %      |

|            |          | 0~2.5*限流电阻   | 1                 |                   | %      |

| LDO & VREF | VS电压     | LDOS[1:0]=01 | 2.35              | 2.45              | V      |

|            | VS温漂     |              | 30                |                   | ppm/°C |

|            | VREF电压   |              | 1.96              | 2.048             | V      |

|            | VREF温漂   |              | 30                |                   | ppm/°C |

| 时钟         | 频率       |              | 5.36              | 5.96              | MHz    |

|            | 频率全温度变化  |              |                   | 2                 | %      |

|            | 频率全电压变化  |              |                   | 1                 | %      |

| 数字         | VIH      |              | 0.7×VDD           | VDD+0.1           | V      |

|            | VIL      |              | GND               | 0.2×VDD           | V      |

|            | VOH      | IoH=1mA      | VDD-0.4           | VDD               | V      |

|            | VOL      | IoL=1mA      | GND               | 0.2+GND           | V      |

|            | III      | VI=VDD       |                   | 1                 | uA     |

|            | III      | VI=GND       | -1                |                   | uA     |

|            | Fsclk    |              |                   | Fosc/4            | MHz    |

| 电源及模块功耗    | 电源电压     | VDD          | 2.4               | 3                 | 3.6    |

|            | LDO工作电流  |              |                   | 160 <sup>2)</sup> | uA     |

|            | VREF工作电流 | 启动温度补偿       |                   | 280 <sup>3)</sup> |        |

|            |          | 不启动温度补偿      |                   | 210 <sup>4)</sup> | uA     |

|            | BIM工作电流  | 正弦波50KHz     |                   | 1.1               | mA     |

|            | OSC工作电流  | Freq=5.96MHz |                   | 78                | uA     |

|            | 数字工作电流   | 正常工作         |                   | 230               | uA     |

|            |          | Power down   |                   | 0.2               | uA     |

| 整体功耗       | BIM应用    | BIM测量模式      | 2.2               | 2.5               | 2.8    |

|            |          |              |                   |                   | mA     |

1):该电流值为限流电阻为 2Kohm 时, 正弦频率为 50KHz 时的典型值; 调节限流电阻可以调节该电流大小, 且电流随正弦频率不同略有差别。

2),3),4):LDO 和 VREF 工作电流均包括了内部 Bandgap 模块的工作电流; 因此两个模块同时打开时, 电流不是简单相加; LDO+VREF (不启动温度补偿) 电流为 260uA。

## 1.6 可靠性指标

- (1) ESD: HBM>=±6kV, Latch up: ±1A;

- (4) 80M~2G 射频干扰, 18 位 ADC 跳动小于 30 个码

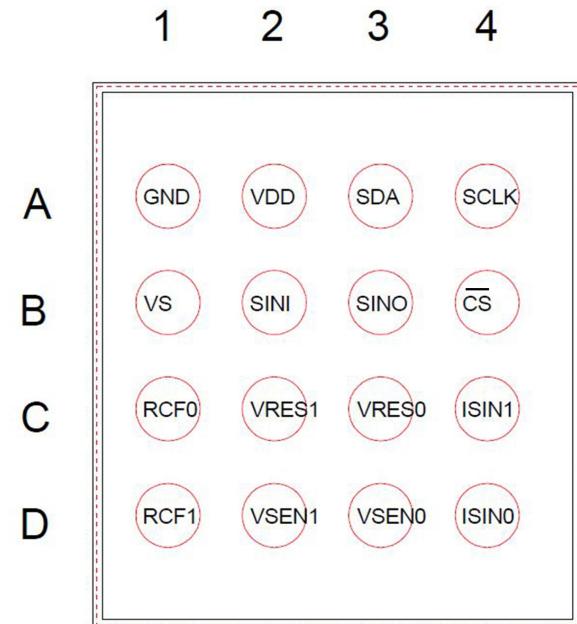

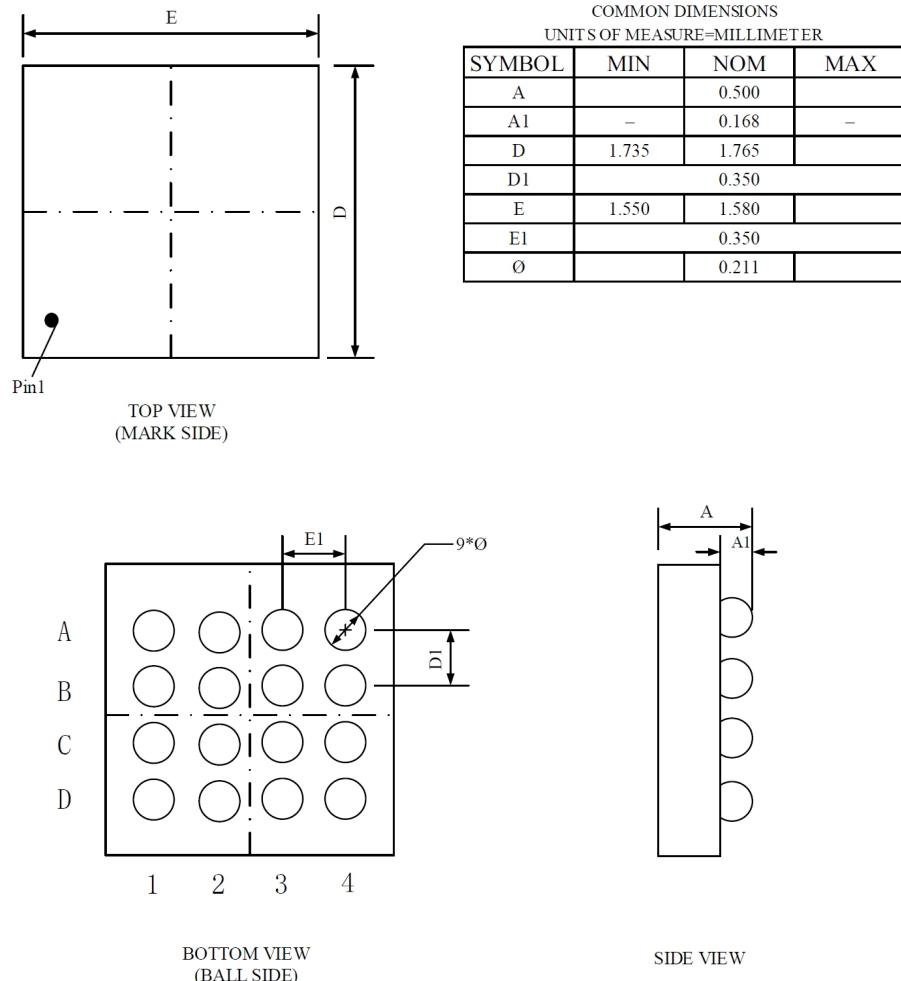

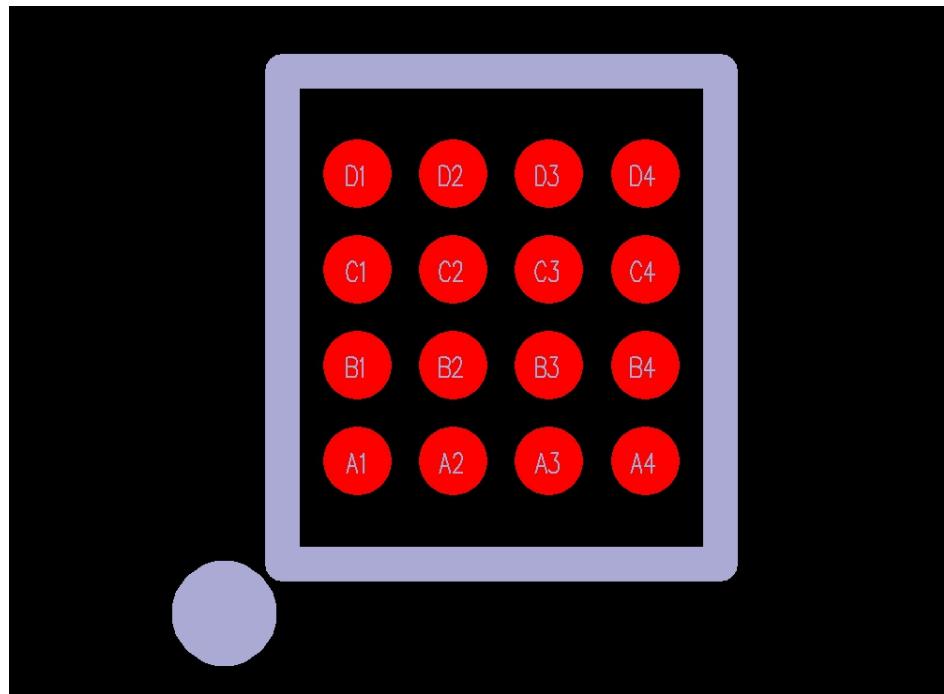

## 1.7 产品型号及引脚

CS1253 具有 4 电极 BIM 测量通道，采用 WLCSP16 封装。

图 1.2 CS1253 引脚图

表 1.3 CS1253 引脚说明

| 引脚序号 | 引脚名称  | 输入/输出 | 说明           |

|------|-------|-------|--------------|

| A2   | VDD   | P     | 电源           |

| A1   | GND   | P     | 地            |

| B1   | VS    | O     | LDO 输出端口     |

| D1   | RCF1  | O     | 整流输出端口 1     |

| C1   | RCF0  | O     | 整流输出端口 0     |

| D2   | VSEN1 | I     | 电压检测电极输入通道 1 |

| D3   | VSEN0 | I     | 电压检测电极输入通道 0 |

| C4   | ISIN1 | O     | 激励电流输出电极通道 1 |

| D4   | ISINO | O     | 激励电流输出电极通道 0 |

| C2   | VRES1 | I     | 参考电阻 1 接入通道  |

| C3   | VRES0 | I     | 参考电阻 0 接入通道  |

| B2   | SINI  | I     | 正弦激励输入端口     |

| B3   | SINO  | O     | 正弦激励输出端口     |

| B4   | CS    | I     | 片选信号端口       |

| A4   | SCLK  | I/O   | 串行通讯时钟端口     |

| A3   | SDA   | I/O   | 串行通讯数据端口     |

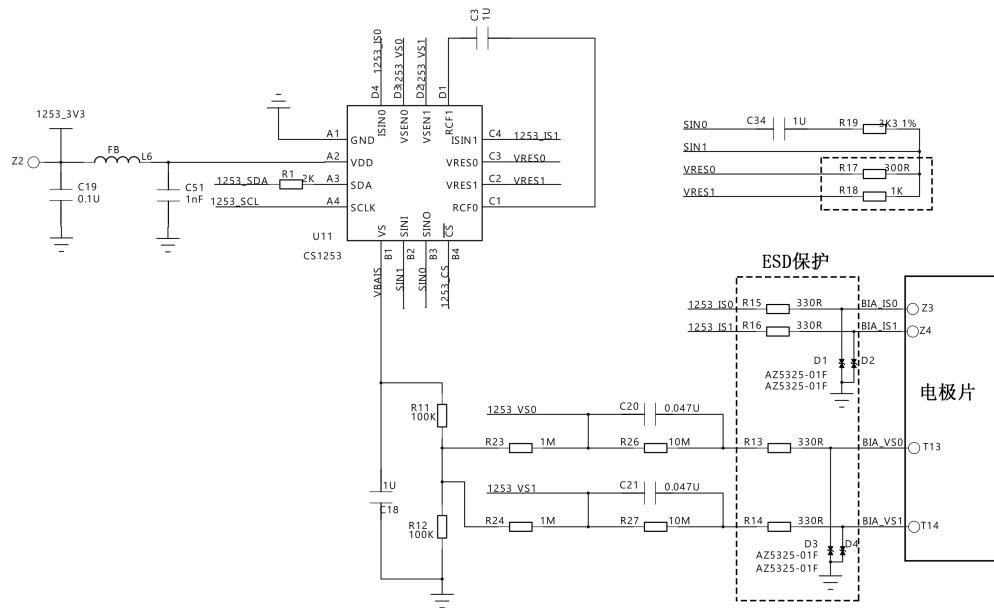

## 1.8 典型应用电路

图 1.3 CS1253 典型应用电路

(该电路图为最小系统配置, 量产电路图请参考相关应用笔记)

## 2 功能寄存器说明

## 2.1 功能寄存器列表

表 2.1 功能寄存器列表

| 寄存器 |      | 比特位        |              |               |            |              |           |            |           | 默认值   |  |  |

|-----|------|------------|--------------|---------------|------------|--------------|-----------|------------|-----------|-------|--|--|

| 地址  | 名称   | BIT7       | BIT 6        | BIT 5         | BIT 4      | BIT 3        | BIT 2     | BIT 1      | BIT 0     |       |  |  |

| 00H | SYS  | TMODE[1:0] |              |               | PMODE[1:0] |              | ENREF     | ENADC      | ENLDO     | ENBIM |  |  |

| 01H | ADC0 | IMOD       | FS SEL       | INNS[2:0]     |            |              | INPS[2:0] |            |           | 00H   |  |  |

| 02H | ADC1 | DR[2:0]    |              |               | BUFBP      | PGA[1:0]     |           |            | ADGN[1:0] |       |  |  |

| 03H | ADC2 | NA         |              |               |            |              |           |            |           |       |  |  |

| 04H | ADC3 | GTCSEL     | GTC[2:0]     |               |            | NA           |           |            |           |       |  |  |

| 05H | ADC4 | CHOPM[1:0] |              | ACCU_NUM[1:0] |            | ADREFS[1:0]  |           | LDOS[1:0]  |           | 40H   |  |  |

| 06H | ADC5 | NA         |              |               |            | REG_NC       | FIL_EN    | FIL_CON1   | FIL_CON0  | 00H   |  |  |

| 07H | BIM0 | ISINO[1:0] |              | ISINI[1:0]    |            | VSENP[1:0]   |           | VSENN[1:0] |           | 00H   |  |  |

| 08H | BIM1 | MIX_EN     | BIMMODE[1:0] |               |            | DACFREQ[3:0] |           |            |           |       |  |  |

| 09H | ADOH |            | ADO[23:16]   |               |            |              |           |            | 00H       |       |  |  |

|     | ADOM | ADOL       | ADO[15:8]    |               |            |              |           |            | 00H       |       |  |  |

|     | ADOL |            | ADO[7:0]     |               |            |              |           |            | 00H       |       |  |  |

| 0AH | ADS  | ADS        | RST          |               |            |              |           |            |           |       |  |  |

## 2.2 功能寄存器说明

### 2.2.1 SYS—系统配置寄存器

表 2.2 SYS 寄存器说明

| Bits  | 描述                                                                                                                                                                                                                                                                                                                                                                                | 权限  | 默认值  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|

| [7:6] | TMODE[7:6] <b>测量模式控制位</b><br>11:BIM 测量模式<br>(置 INPS[2:0]=110, INNS[2:0]=110, LVSIFT=0, PGA[1:0]=00, BUFBP=0, ADGN[1:0]=00, ADREFS[1:0]=00, FS_SEL=0, IMOD=0, 相应寄存器配置无效;其他由寄存器决定)<br>10:电源电压测量模式<br>(置 ENREF=1, INPS[2:0]=100, INNS[2:0]=100, LVSIFT=0, PGA[1:0]=00, BUFBP=0, ADGN[1:0]=00, ADREFS[1:0]=10, FS_SEL=0, IMOD=0, 相应寄存器配置无效;其他由寄存器决定)<br>01:N/A<br>00:手动测量模式<br>(自由配置) | r/w | 00'b |

| [5:4] | PMODE[1:0] <b>工作模式控制位(仅在 TMODE=00 时)</b><br>11:自由模式<br>(ADC 自由配置)<br>10:占空比模式, DR=640Hz<br>(FS_SEL=0, BUFBP=0, IMOD=0, ENADC 和 ENLDO 受控制)<br>01:性能模式<br>(FS_SEL=1, BUFBP=0, IMOD=1, 相应寄存器配置无效;其他配置由相应寄存器决定)<br>00:普通模式 (当前不可用)<br>(FS_SEL=0, BUFBP=1, IMOD=0, 相应寄存器配置无效;其他配置由相应寄存器决定)                                                                                             | r/w | 00'b |

| [3]   | ENREF <b>VREF 模块使能信号</b><br>1:VREF 使能<br>0:VREF 关闭                                                                                                                                                                                                                                                                                                                                | r/w | 0'b  |

| [2]   | ENADC <b>ADC 模块使能位</b><br>1:ADC 使能<br>0:ADC 关闭                                                                                                                                                                                                                                                                                                                                    | r/w | 0'b  |

| [1]   | ENLDO <b>LDO 模块使能位</b><br>1:LDO 使能<br>0:LDO 关闭                                                                                                                                                                                                                                                                                                                                    | r/w | 0'b  |

| [0]   | ENBIM <b>BIM 模块使能位</b><br>1:BIM 使能<br>0:BIM 关闭                                                                                                                                                                                                                                                                                                                                    | r/w | 0'b  |

### 2.2.2 ADC0—ADC 配置寄存器

表 2.3 ADC0 寄存器说明

| Bits  | 描述                                                         | 权限  | 默认值   |

|-------|------------------------------------------------------------|-----|-------|

| [7]   | IMOD <b>调制器 MOD 电流控制位</b><br>1:性能模式电流=普通模式电流×2<br>0:普通模式电流 | r/w | 0'b   |

| [6]   | FS_SEL <b>采样频率选择位</b><br>1:662.22KHz<br>0:331.11KHz        | r/w | 0'b   |

| [5:3] | INNS[2:0] <b>PGA 负端输入信号选择位</b><br>111:N/A                  | r/w | 000'b |

|       |           |                                                                                                                                  |     |       |

|-------|-----------|----------------------------------------------------------------------------------------------------------------------------------|-----|-------|

|       |           | 110:BIMN (仅在 TMODE=11 时有效)<br>101:1/2 VS (共模电压)<br>100:GND (仅在 TMODE=10 有效)<br>011~000:NA                                        |     |       |

| [2:0] | INPS[2:0] | <b>PGA 正端输入信号选择位</b><br>111:N/A<br>110:BIMP (仅在 TMODE=11 时有效)<br>101:1/2 VS (共模电压)<br>100:1/8 VDD (仅在 TMODE=10 有效)<br>011~000:NA | r/w | 000'b |

### 2.2.3 ADC1—ADC 配置寄存器 1

表 2.4 ADC1 寄存器说明

| Bits  | 描述        |                                                                                                                         | 权限  | 默认值   |

|-------|-----------|-------------------------------------------------------------------------------------------------------------------------|-----|-------|

| [7:5] | DR[2:0]   | <b>ADC 输出速率选择位</b><br>111:1280Hz<br>110:640Hz<br>101:320Hz<br>100:160Hz<br>011:80Hz<br>010:40Hz<br>001:20Hz<br>000:10Hz | r/w | 000'b |

| [4]   | BUFBP     | <b>Buffer 控制位</b><br>1:Buffer 关闭 (当前不可用)<br>0:Buffer 开启                                                                 | r/w | 0'b   |

| [3:2] | PGA[1:0]  | <b>PGA 增益选择位</b><br>11:Gain =32<br>10:Gain=16<br>01:Gain=1<br>00:Gain=1                                                 | r/w | 00'b  |

| [1:0] | ADGN[1:0] | <b>调制器增益选择位</b><br>11:Gain=8 (DR 下降为 1/4)<br>10:Gain=4 (DR 下降为 1/2)<br>01:Gain=2<br>00:Gain=1                           | r/w | 00'b  |

### 2.2.4 ADC3—ADC 配置寄存器 3

表 2.6 ADC3 寄存器说明

| Bits  | 描述       |                                                                                                | 权限  | 默认值  |

|-------|----------|------------------------------------------------------------------------------------------------|-----|------|

| [7]   | GTCSEL   | <b>增益温漂补偿粗细选择位:</b><br>1:粗调=精调×6, 用于补偿传感器温漂<br>0:精调, 用于调整芯片自身温漂                                | r/w | 00'b |

| [6:4] | GTC[2:0] | <b>增益温漂补偿选择位(CTCSL=0):</b><br>111:15 ppm/°C<br>110:10 ppm/°C<br>101:5 ppm/°C<br>100:0<br>000:0 | r/w | 00'b |

|       |  |                                                   |  |  |

|-------|--|---------------------------------------------------|--|--|

|       |  | 001:-5 ppm/°C<br>010:-10 ppm/°C<br>011:-15 ppm/°C |  |  |

| [3:0] |  | NA                                                |  |  |

## 2.2.5 ADC4—ADC 配置寄存器 4

表 2.7 ADC4 寄存器说明

| Bits     | 描述             | 权限                                                                                                                                                                                                                                                                                                                         | 默认值      |      |    |   |    |    |    |    |    |    |     |      |

|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------|----|---|----|----|----|----|----|----|-----|------|

| [7:6]    | CHOPM[1:0]     | 仪放(IA)及调制器(MOD)斩波频率控制位<br>11: 仪放斩波频率为 fs_clk/64, 调制器斩波频率为 fs_clk/128<br>10: 仪放斩波频率为 fs_clk/32, 调制器斩波频率为 fs_clk/128<br>01: 仪放斩波频率为 fs_clk/32, 调制器斩波频率为 fs_clk/256<br>00: 不开斩波<br>fs_clk 为 MOD 采样频率                                                                                                                          | r/w      | 01'b |    |   |    |    |    |    |    |    |     |      |

| [5:4]    | ACCU_NUM [1:0] | 占空比模式下 COMB 数据累加个数选择<br><table border="1" data-bbox="595 932 1127 1111"> <tr> <th>ACCU_NUM</th> <th>累加个数</th> </tr> <tr> <td>00</td> <td>8</td> </tr> <tr> <td>01</td> <td>16</td> </tr> <tr> <td>10</td> <td>32</td> </tr> <tr> <td>11</td> <td>64</td> </tr> </table><br>注意: (COMB 数据累加个数+4)*ADC 输出速率不能大于 COMB 速率 640Hz。 | ACCU_NUM | 累加个数 | 00 | 8 | 01 | 16 | 10 | 32 | 11 | 64 | r/w | 00'b |

| ACCU_NUM | 累加个数           |                                                                                                                                                                                                                                                                                                                            |          |      |    |   |    |    |    |    |    |    |     |      |

| 00       | 8              |                                                                                                                                                                                                                                                                                                                            |          |      |    |   |    |    |    |    |    |    |     |      |

| 01       | 16             |                                                                                                                                                                                                                                                                                                                            |          |      |    |   |    |    |    |    |    |    |     |      |

| 10       | 32             |                                                                                                                                                                                                                                                                                                                            |          |      |    |   |    |    |    |    |    |    |     |      |

| 11       | 64             |                                                                                                                                                                                                                                                                                                                            |          |      |    |   |    |    |    |    |    |    |     |      |

| [3:2]    | ADREFS[1:0]    | ADC 参考电压选择位<br>11: 正参考=内部 VREF, 负参考=GND<br>10: 正参考=内部 VREF, 负参考=GND<br>01: 正参考=VREF 外接 REFP 再接回 ADC<br>负参考=外部 REFN<br>00: 正参考=外部 REFP, 负参考=外部 REFN                                                                                                                                                                         | r/w      | 00'b |    |   |    |    |    |    |    |    |     |      |

| [1:0]    | LDOS [1:0]     | 内部 LDO 输出 VS 电压选择位<br>11: 3.0V<br>10: 2.8V<br>01: 2.45V<br>00: 2.35V                                                                                                                                                                                                                                                       | r/w      | 00'b |    |   |    |    |    |    |    |    |     |      |

## 2.2.6 ADC5—ADC 配置寄存器 5

表 2.8 ADC5 寄存器说明

| Bits  | 描述     | 权限                                                                                             | 默认值 |      |

|-------|--------|------------------------------------------------------------------------------------------------|-----|------|

| [7:4] | NA     |                                                                                                |     |      |

| [3]   | REG_NC | 保留位                                                                                            |     |      |

| [2]   | FIL_EN | COMB 之后的低通滤波器使能控制信号<br>1: 滤波器打开<br>0: 滤波器关闭<br>注: 在占空比模式下不可以使用; 速率为 10Hz、20Hz、40Hz、80Hz 不可以使用。 | r/w | 00'b |

|     |          |                                               |     |     |

|-----|----------|-----------------------------------------------|-----|-----|

| [1] | FIL_CON1 | <b>滤波器级联控制</b><br>0:滤波器使用级联结构<br>1:滤波器不使用级联结构 | r/w | 0'b |

| [0] | FIL_CON2 | <b>滤波器系数控制</b><br>0:使用系数 1<br>1:使用系数 2        | r/w | 0'b |

### 2.2.7 BIM0— BIM 配置寄存器 0

表 2.9 BIM0 寄存器说明

| Bits  | 描述         |                                                              | 权限  | 默认值  |

|-------|------------|--------------------------------------------------------------|-----|------|

| [7:6] | ISINO[1:0] | <b>正弦激励电流输出通道选择位</b><br>Others: NA<br>01:ISIN1<br>00: ISIN0  | r/w | 00'b |

| [5:4] | ISINI[1:0] | <b>正弦激励电流接收 通道选择位</b><br>Others: NA<br>01:ISIN1<br>00: ISIN0 | r/w | 00'b |

| [3:2] | VSENP[1:0] | <b>电压检测正电极通道选择位</b><br>Others: NA<br>01:VSEN1<br>00:VSEN0    | r/w | 00'b |

| [1:0] | VSENN[1:0] | <b>电压检测负电极通道选择位</b><br>Others: NA<br>01:VSEN1<br>00:VSEN0    | r/w | 00'b |

### 2.2.8 BIM1— BIM 配置寄存器

表 2.10 BIM1 寄存器说明

| Bits  | 描述            |                                                                                                   | 权限  | 默认值    |

|-------|---------------|---------------------------------------------------------------------------------------------------|-----|--------|

| [7]   | NA            |                                                                                                   | r/w | 0'b    |

| [6]   | MIX_EN        | <b>解调模式选择位</b><br>1:MIX 解调模式<br>0:全波整流模式                                                          | r/w | 0'b    |

| [5:4] | BIMMODE [1:0] | <b>BIM 模式选择位</b><br>11:内短模式<br>10:校准电阻 1 模式<br>01:校准电阻 0 模式<br>00:测量模式                            | r/w | 00'b   |

| [3:0] | DACFREQ[3:0]  | <b>正弦电流输出频率选择位</b><br>101:250KHz<br>100:100KHz<br>011:50KHz<br>010:25KHz<br>001:10KHz<br>000:5KHz | r/w | 0000'b |

### 2.2.9 ADO—ADC 转换数据寄存器

表 2.11 ADO 寄存器说明

| Bits      | 描述         |                  | 权限 | 默认值 |

|-----------|------------|------------------|----|-----|

| ADOH[7:0] | ADO[23:16] | ADC 转换值的[23:16]位 | r  | 00H |

| ADOM[7:0] | ADO[15:8]  | ADC 转换值的[15:8]位  | r  | 00H |

| ADOL[7:0] | ADO[7:0]   | ADC 转换值的[7:0]位   | r  | 00H |

### 2.2.10 ADS—ADC 转换数据读取标准寄存器

表 2.12 ADO 寄存器说明

| Bits  | 描述  |                                                  | 权限 | 默认值      |

|-------|-----|--------------------------------------------------|----|----------|

| [7]   | ADS | <b>ADO 中数据读取标志</b><br>1:数据已经被读取<br>0:数据尚未被读取     | r  | 0'b      |

| [6]   | RST | <b>芯片上电复位标志位</b><br>1:芯片上电复位完成<br>0:用户查询该标志后自动清零 | r  | 0'b      |

| [5:0] | NA  |                                                  |    | 000000'b |

## 3 功能描述

### 3.1 输入选择

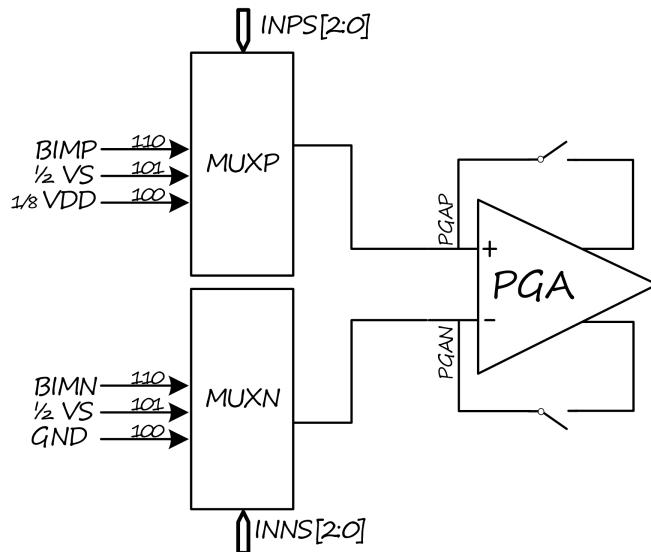

CS1253 中模拟输入通道及内部若干信号分别通过 MUXP 和 MUXN 后，接到 PGA 正端和负端，如图 3.1 所示。

图 3.1 模拟输入结构图

1/8 VDD 和 GND 配对进行电源电压测量；1/2 VS 用于内短进行失调校正；

BIMP/BIMN 是来自 BIM 模块的差分信号。

### 3.2 PGA 和 ADC

CS1253 通过一个低噪声，低漂移的 PGA 放大器将输入信号放大后送入一个 2 阶的 Sigma-Delta ADC 进行模数转换。如图 3.2 所示为 PGA 和 ADC 的结构图，其中 PGA 的增益由 PGA[1:0]选择，具有 1\8\16\32 四档可选；ADC 的增益由 ADGN[1:0]所选择、具有 1\2\4\8 四档可选；另外 ADC 参考电压来自输入的 REFP-REFN。

图 3.2 PGA 和 ADC 结构图

输入信号的增益 Gain 由 PGA 和 ADC 各自增益的乘积决定。

$$Gain = PGA \times ADGN \quad (式 3-1)$$

为了提高信号的建立表现，PGA 输出到 ADC 调制器输入还有 Buffer 作为缓冲；但同时提供 Buffer 旁路功能，将 BUFBP 置'1'，则 Buffer 被旁路，PGA 输出信号直接接入 ADC 的调制器。CS1253 的差分满幅输入范围 FS 由 Gain 决定，

$$FS = (REFP - REFN) / Gain \quad (式 3-2)$$

若差分输入通道  $AIN_p - AIN_n = VIN$ ，则为保证不溢出， $VIN$  的范围必须小于  $FS$ 。

CS1253 的 ADC 采用 2 阶 sigma-delta 调制器实现，内部采样频率为 331.11KHz(普通模式)或 662.22KHz(性能模式)；增益  $ADGN$  可由电容倍增和频率倍增实现。

CS1253 的 ADC 带有内部增益温漂补偿功能，通过  $GTC_{SL}$  以及  $GTC[2:0]$  可以配置。当  $GTC_{SL}=1$  时为粗调档，此时对应  $GTC[2:0]$  增益温漂补偿的一个步长为  $30\text{ppm}/^\circ\text{C}$ ，可用于补偿外部传感器的温漂；而当  $GTC_{SL}=0$  时，相应步长为  $5\text{ppm}/^\circ\text{C}$ ，可用于调整芯片内部的增益温漂。

### 3.3 数字滤波器

从 Sigma-delta ADC 出来的数据是 1 位的高速比特流数据，并且包含了大量的高频噪声，因此需要数字滤波器对该比特流数据进行滤波和比特率转换，将高频噪声滤除、同时完成降采样，将 1 位高速比特流数据变成 24-bit 的二进制码数据。这个工作通过多阶的 COMB 滤波器完成。COMB 滤波器之后可以选择是否使用滤波器进一步进行滤波。

#### 3.3.1 频率响应

图 3.3 COMB 滤波器的频率响应特性( $F_s=331\text{Hz}$ ,  $DR=10\text{Hz}$ , 3 阶 COMB)

#### 3.3.2 建立时间

正常模式下数字 COMB 在低速是 3 阶(10Hz、20Hz、40Hz、80Hz)，高速时是 4 阶或 5 阶(160Hz、320Hz、640Hz、1280Hz)；占空比模式下，数字 COMB 是 4 阶或 5 阶。数据建立时间跟 COMB 的阶数有关，3 阶 COMB 的数据在第三个能够建立好；4 阶 COMB 的数据在第四个能够建立好；5 阶 COMB 的数据在第五个能够建立好。

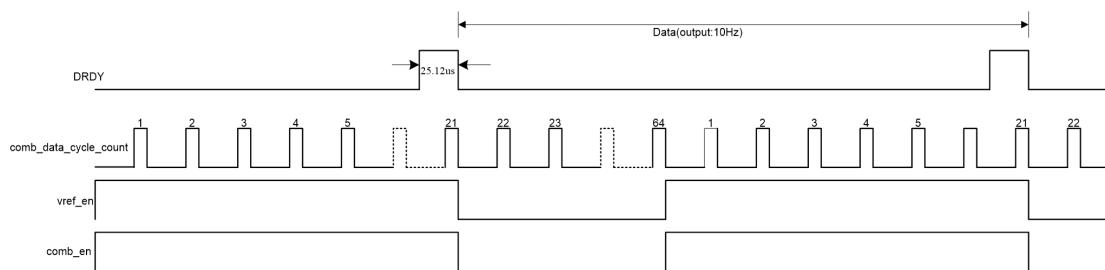

图 3.4 COMB 建立过程

如果 FIL\_EN 设置为 1，数据建立时间更长，所需时间如下表所示（数据误差收敛到在万分之一以内的时间）。

| FILCON1 | FILCON0 | 建立时间              |

|---------|---------|-------------------|

| 0       | 0       | COMB 数据建立时间+300ms |

| 0       | 1       | COMB 数据建立时间+590ms |

| 1       | 0       | COMB 数据建立时间+230ms |

| 1       | 1       | COMB 数据建立时间+460ms |

### 3.4 人体阻抗测量

人体阻抗测量的原理是将人体等效为一个阻容网络，然后让一路电流流过该网络产生一个和网络阻抗成正比的压降，通过 ADC 测得该压降即可换算出阻容网络的等效阻抗；然后通过查询一个表格，将人体等效阻抗换算成人体的组成成分。这个表格通常和人的年龄、性别、身高体重、以及人种有关。(关于人体等效阻抗的阻容网络模型、各成分的电学模型、人体阻抗和人体脂肪含量的关系、以及分段测量、多频率测量原理等请参考人体阻抗测量的相关专业知识)。本芯片内部集成了一个交流人体阻抗测量(BIM)模块。

图 3.5 BIM 模块结构图

图 3.5 所示为 BIM 的模块结构图，其中正弦信号发生器（包括 DDS、DAC、LPF 等）可以产生正弦波信号，该信号经过 C0、R0 做高通滤波及限流后转换为正弦电流，并通过至少一对激励电极（端口 ISINx， $x=0,1$ ，安装在人体不同的两个部位，一个负责发射正弦电流激励信号，一个负责接受该激励信号）在人体的等效阻容网络上形成一个电压降；通过测量电极（端口 VSENy， $y=0,1$ ）探知该电压降信号后，芯片内部对其进行整流滤波等处理，然后送入 ADC 中测量将模拟电压信号转换为数字信号，从而得到人体阻抗上的电压降值。

#### 3.4.1 正弦信号发生器

如图 3.5 BIM 模块结构图所示，正弦信号发生器包括一个直接数字合成器（DDS）、DAC 以及 LPF 低通滤波器；其中 DDS 可以生成正弦波码值序列驱动一个 1-MSPS/6-bit 的 DAC；而 DAC 输出送入一个两阶滤波器，截至频率约 150KHz 的 LPF 中进行滤波，以消除高次谐波；LPF 的输出接一个外部电容 C0 进行隔直，避免有直流电流流入人体，再通过一个限流电阻 R0 接到内部运算放大器 OPA1 的负输入端，将电压信号转换为电流信号，同时将电流限定在安全值 500uA 以内。设激励电流为  $I(t)$ ，DAC 输出电压为  $VDAC$ ，正弦波幅度为  $AMP$ ，角频率为  $\omega_0$ ，

$$I(t) = VDAC / R0 = AMP \cdot \sin(\omega_0 \cdot t) \quad (式 3-7)$$

若电阻  $R0$  具有  $\pm 20\%$  的容差，通常可将  $R0$  设置为 2Kohm，此时输出电流的 RMS 属于安全区域。减小  $R0$  可以增大电流，提高增益，但要考虑电流对人体的作用。通常平均电流达到 1mA 时，人体将有所感觉。另外，电容  $C0$  可以选择 10uF（推荐）或 1uF 等。

正弦波频率通过  $DACFREQ[3:0]$  配置，支持 5KHz、10KHz、25KHz、50KHz、100KHz、250KHz 等频率。

### 3.4.2 激励电极及测量电极

激励电极  $ISIN3\sim ISINO$  可通过 MUX 任意组合成发射电极-接收电极对，用于将激励电流信号  $I(t)$  从一端注入人体，然后在另一端接收；  $ISINO[1:0]$  控制 MUX 可将任一激励电极接 OPA1 的输入负端作为发射电极，而  $ISINI[1:0]$  控制 MUX 可将任一激励电极接入 OPA1 的输出端作为接收电极，但发射和接收电极不能为同一电极。

在发射电极和接收电极之间是人体等效阻抗  $Z$ ，流过  $I(t)$  后形成一个压降  $V(t)$ ，

$$V(t) = I(t) \cdot Z = A|Z| * \sin(\omega_0 \cdot t + \theta) \quad (式 3-8)$$

其中  $|Z|$  是等效阻抗  $Z$  的绝对值， $\theta$  是等效阻抗  $Z$  的相角。对于纯阻性阻抗， $\theta = 0$ 。测量电极  $VSEN3\sim VSEN0$  可通过 MUX 任意组合成正负测量电极测得上述电压  $V(t)$ ；其中正测量电极接入差分运放 OPA2 的正输入端，可通过  $VSEN[1:0]$  进行配置；负测量电极接入差分运放 OPA2 的负输入端，可通过  $VSENN[1:0]$  进行配置。

### 3.4.3 整流

电压信号  $V(t)$  经过差分运放 OPA2 处理后变成一对差分正弦信号送入全波整流模块  $Recf$ ，经整流后再通过  $RCF0$  和  $RCF1$  外接电容滤波，产生 DC 信号送入  $MUXP/MUXN$ ，进入 ADC 信号链进行测量。在处理的过程中，包括 LPF 环节，会对电流  $I(t)$  和电压  $V(t)$  的幅值有调整，总括起来形成一个增益  $G0$ ，换算到最后整流后的有效值中。

当采用全波整流(FWR)模式时，整流后的电压有效值  $V_{rms}$  为：

$$V_{rms,f} = |I(t) \cdot Z| = G0 \cdot AMP \cdot |Z| / \pi \quad (式 3-9)$$

当采用 MIX 整流(MIX)模式时，整流后的电压有效值  $V_{rms}$  为：

$$V_{rms,m} = |I(t) \bullet Z| = (G0 \bullet AMP \bullet |Z|/\pi) \bullet \cos \theta \quad (式 3-10)$$

因此，对于只需要知道阻抗绝对值的场景，采用 FWR 模式得到  $V_{rms,f}$  值即可换算得到  $|Z|$ ；对于既需要知道阻抗绝对值又希望了解相角变化的场景，可以在采用 FWR 基础上，再使用 MIX 模式得到  $V_{rms,m}$ ，

$$\cos \theta = V_{rms,m} / V_{rms,f} \quad (式 3-11)$$

因为人体阻抗网络是阻容网络，因此  $\theta < 0$ ，所以

$$\theta = -\arccos(V_{rms,m} / V_{rms,f}) \quad (式 3-12)$$

#### 3.4.4 阻抗校准

由于非理想因素存在，BIM 在使用前需要校准信号增益和失调。通过 BIMD[1:0]可以调整 BIM 模式，从测量模式切换到校准模式。

在校准电阻 0 模式下，在 SINO 和 VRES0 之间接电阻  $Rsd0$ ，经过 BIM 信号链和 ADC 信号链后，ADC 可以测得的电压有效值：

$$V_{rms,0} = Kb \bullet Rsd0 + V_{os} \quad (式 3-13)$$

在校准电阻 1 模式下，在 SINO 和 VRES0 之间接电阻  $Rsd1$ ，经过 BIM 信号链和 ADC 信号链后，ADC 可以测得的电压为：

$$V_{rms,1} = Kb \bullet Rsd1 + V_{os} \quad (式 3-14)$$

式 3-13 和式 3-14 中  $V_{os}$  为失调电压，可在内短模式下测得；而  $Kb$  表示信号增益，理想情况下(MIX 模式和 FWR 模式存在微小区别，高精度要求场合可分别校正)，

$$Kb = (G0 \bullet AMP / \pi) \quad (式 3-15)$$

但实际上由于  $G0$  随着工艺偏差、信号频率都有变化，因此需要通过联立两方程求得  $Kb$ ，用于人体等效阻抗的计算，因

$$Kb = [(V_{rms,1} - V_{os}) - (V_{rms,0} - V_{os})] / (Rsd1 - Rsd2) \quad (式 3-16)$$

得到了  $V_{os}$  及  $Kb$  的值后，对于实际阻抗  $Z$ ，则有

$$V_{rms,f} = Kb_f \bullet |Z| + V_{os,f} \quad (\text{FWR 模式})$$

$$V_{rms,m} = Kb_m \bullet |Z| \bullet \cos \theta + V_{os,m} \quad (\text{MIX 模式})$$

求得：

$$|Z| = (V_{rms,f} - V_{os,f}) / Kb_f \quad (式 3-17)$$

$$\theta = -\arccos[(V_{rms,m} - V_{os,m}) / (V_{rms,f} - V_{os,f}) \bullet (Kb_f / Kb_m)] \quad (式 3-18)$$

1)当前版本  $Kb$  需要加 0.005 的校正因子

### 3.5 参考电压源

CS1253 内部集成一个低漂移的 LDO，可以输出电压给 VS，具有 4 档可选，其中 2.35V/2.45V/2.8V/3.0V 主要提供给 VS 使用，用于给内部 ADC 部分供电，负载电流最大 10mA。为保证 VS 正常输出，VDD 需要比 VS 电压高 100mV 以上。典型的温漂系数为 30ppm/°C(-40~85°C)。还包括一个内部参考电压源 VREF，输出为 2.048V，主要用于做测量的参考电压提供给 REFP（外接电容提高精度）或者作为内部参考电压 VREF，典型的温漂系数为 30ppm/°C(-40~85°C)，仅作参考电压，无负载能力。

### 3.6 内部时钟源

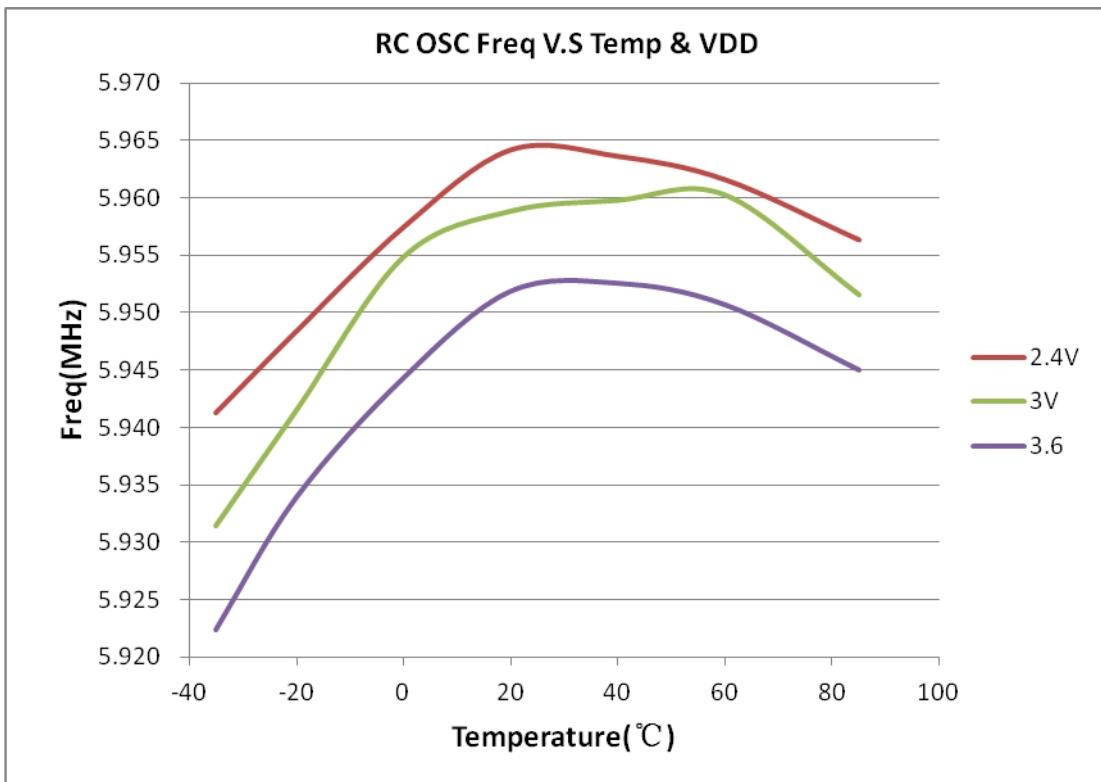

CS1253 内部提供一个低漂移的 RC 时钟，时钟频率为 **5.96MHz**，在 -40~85°C 变化范围内漂移小于 2%，在 2.4~3.6V 的 VDD 电压范围内，变化小于 1%。

### 3.7 测量模式及其切换

CS1253 内部具有多个模拟信号通道，包括 BIM 信号、电源电压信号以及内短。选择不同的输入信号时，通常涉及到通道切换、增益设置、输出速率选择等操作，需要 2~3 条操作指令才能完成配置，切换回来也需要同样的操作指令，上位机软件设计较为繁琐。CS1253 内部有三种不同类型输入信号，加上外部输入信号，则有多达四种输入信号需要处理，在某些应用环境下，例如称重和 BIM 测量应用下，需要频繁在称重和 BIM 测量之间切换，每次切换上位机都要发送 4~6 条指令，较为不便。为了简化软件设计，本芯片内部设计了单命令切换测量模式的结构，通过配置 TMODE[1:0] 寄存器在电源电压测量、BIM 测量以及手动模式之间切换。前两种模式下，通道选择、增益配置及输出速率三个参数都是内部固定配置好，不需要用户干预，手动模式下用户可以随意配置相关参数；手动模式下切换至其余任意模式再切换回手动模式时，用户的设置保持不变。

### 3.8 多种工作模式

CS1253 提供了多种工作模式可以选择，包括性能模式、正常模式、低功耗模式。

性能模式下，PGA 中 Buffer 打开，ADC 调制器的采样频率为 662.22KHz，此时 ADC 信号链精度最高，增益温漂、线性表现最好，同时 ADC 信号链功耗达到 1.5mA，可应用于需要 10Hz SPS，10000 点以上分度的测量场合。正常模式对性能和功耗进行了平衡，Buffer 旁路，采样频率降低为 331.11KHz，可应用于 10000 分度以下测量场合（例如人体称重），ADC 信号链功耗为 1.2mA。低功耗模式是采用占空比的方式来达到节省功耗的目的。在一个 10Hz 数据更新频率的周期内，数字滤波器以 640Hz 的输出速率工作，开启 ADC 后丢弃前 5 个数据，然后累加相应个数进行平均。

占空比模式下 VREF 输出和数字电路间歇性工作，以降低芯片功耗。

在占空比模式下，COMB 是 4 阶的，工作在高速，SPI 数据输出速率只有 10Hz，COMB 数据输出速率为 640Hz，64 个 COMB 周期 SPI 才输出一个数据，我们可以使 COMB 只输出前 21 个数据(COMB 前 5 个数据丢失，累加 16 个数据平均输出(第 6 个到第 21 个))，后面 43 个数据周期关闭 COMB 和 VREF 输出，示意图如下。

图 3.8 CS1253 低功耗工作示意图

注：COMB 数据输出速率和累加数据个数可以配置。

### 3.9 复位和断电(POR&power down)

当芯片上电时，内置上电复位电路会产生复位信号，使芯片自动复位。

当 SCLK 从低电平变高电平并保持在高电平超过  $172\mu\text{s}$ ，CS1253 即进入 PowerDown 模式。当 SCLK 重新回到低电平时，芯片会重新进入正常工作状态。

当系统由 Power down 重新进入正常工作模式时，此时所有功能配置为 PowerDown 之前的状态，不需要进行功能配置。

## 4 转换有效位

表 4.1 ADC 信号链不同配置下的有效位(ENOB)

| PGA | ADGN | BUFBP | PMODE | TMODE | DR   | ENOB |

|-----|------|-------|-------|-------|------|------|

| 32  | 2    | ON    | 00    | 00    | 10Hz | TBD  |

| 32  | 2    | OFF   | 01    | 00    | 10Hz | 20.8 |

| 32  | 2    | OFF   | 10    | 00    | 10Hz | TBD  |

| x   | x    | x     | xx    | 01    | 10Hz | 19.5 |

| x   | x    | x     | xx    | 10    | 10Hz | 18.2 |

| x   | x    | x     | xx    | 11    | 10Hz | 21.2 |

## 5 典型特性

### 5.1 LDO 典型特性

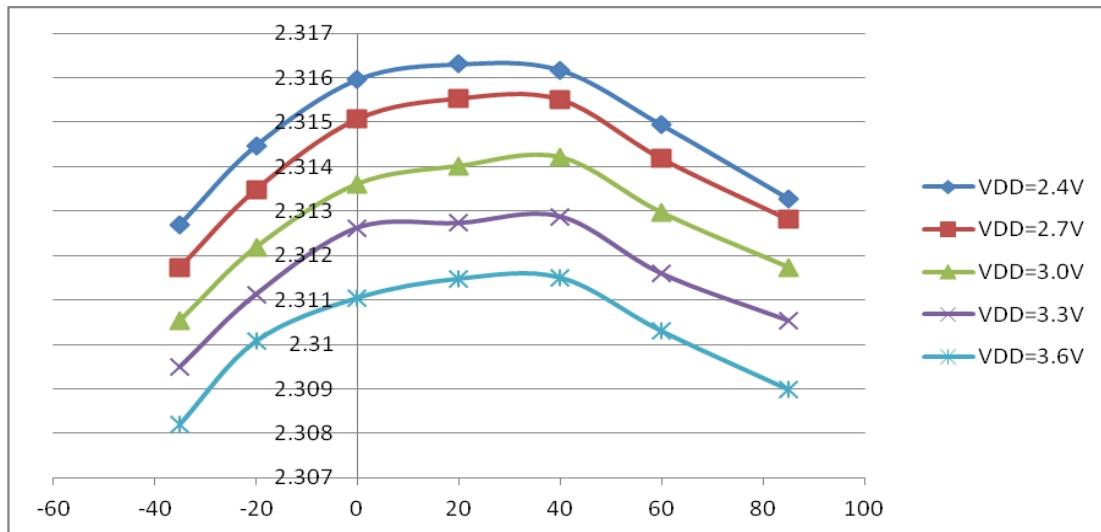

图 5.1 LDO 全电压全温度范围的典型特性(LDOS[1:0]=00, 负载 1mA)

### 5.2 内部时钟典型特性

图 5.2 内部时钟全电压全温度范围的典型特性

### 5.3 BIM 典型特性

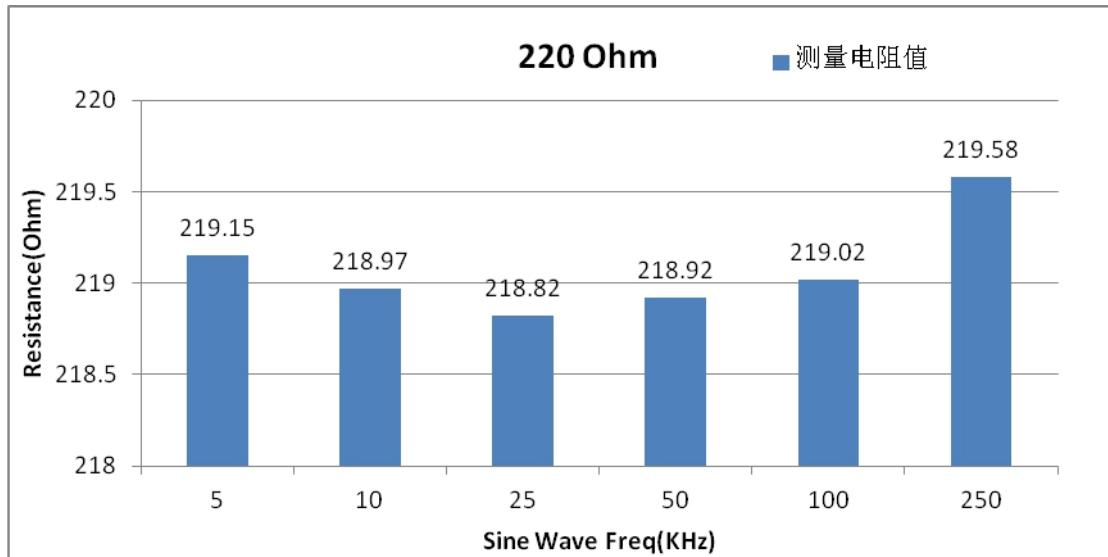

图 5.3 FWR 模式下 220 欧姆纯电阻网络的测试结果

图 5.4 FWR 模式下 1000 欧姆纯电阻网络的测试结果

图 5.5 FWR 模式下 1958 欧姆纯电阻网络的测试结果

图 5.6 FWR+MIX 模式 510ohm+470pF 并联网络的阻抗绝对值测试结果

图 5.7 FWR+MIX 模式 510ohm+470pF 并联网络的相位角测试结果

图 5.8 FWR+MIX 模式 1018Ohm+10nF 并联网络的阻抗绝对值测试结果

图 5.9 FWR+MIX 模式 1018Ohm+10nF 并联网络的相位角测试结果

## 6 三线串行通讯接口

CS1253 中，采用 3 线串行通信，其中  $\overline{CS}$  为片选/复位信号，SCLK 为通讯时钟、SDA 是双向数据线及数据转换完成标志。

$\overline{CS}$ : 串行接口片选信号，低电平有效，输入信号，内部悬空，建议外接上拉电阻； $\overline{CS}$  由高电平变为低电平时，表示当前芯片被选中，处于通讯状态； $\overline{CS}$  由低变电平变为高电平，表示通讯结束，通讯口复位处于空闲状态。

SCLK: 串行时钟输入脚，决定数据移出或移入 SPI 口的传输速率。所有的数据传输操作均与 SCLK 同步，在上升沿将数据从 SDA 引脚输出；在下降沿读取 SDA 上的数据。

SDA: 串行数据输入/输出脚。 $\overline{CS}=1$ ，SDA 输出 DRDY，表示 ADC 转换数据已准备好； $\overline{CS}=0$ ，SDA 串行通讯数据端口。

串行通讯的命令寄存器是一个 8bit 宽的寄存器。对于读写操作，命令寄存器的 bit7 用来确定本次数据传输操作的类型是读操作还是写操作，命令寄存器的 bit6-0 是读写的寄存器的地址。对于特殊命令操作，命令寄存器的 bit7-0 固定为 0xEA。

注：当 SCLK 保持低电平 687us 左右进入通讯复位模式（只复位串行通讯接口，防止串行通讯接口进入异常无法通讯，不复位芯片）。

表 6.1 串口通讯命令列表

| 命令名称 | 命令寄存器            | 数据         | 描述                                             |

|------|------------------|------------|------------------------------------------------|

| 读命令  | {0,REG_ADR[6:0]} | Read_Data  | 从地址为 REG_ADR[6:0]的寄存器中读数据。<br>注：读无效地址，返回值为 00h |

| 写命令  | {1,REG_ADR[6:0]} | Write_Data | 向地址为 REG_ADR[6:0]的寄存器中写数据                      |

| 复位指令 | 0xEA             | 0x96       | 复位指令，接收到指令之后，芯片复位。                             |

### 6.1.1 读时序

工作过程：

外部设备在CS有效后，先通过SDA写入读命令字节，CS1253接收到读命令后，在SCLK的上升沿将数据按位从SDA引脚输出。注意：

- 1).以字节为单位传输，高比特位在前，低比特位在后；

- 2).多字节寄存器，先输出高字节内容，再传输低字节内容；

- 3).外部设备在SCLK上升沿写命令字节，CS1253在SCLK上升沿将数据从SDA输出；

- 4).数据字节之间的时间t1要大于等于2个系统时钟周期；

- 5).最后一个字节的LSB传送完毕，CS由低变高结束数据传输。SCLK下降沿和CS上升沿之间的时间t2要大于等于2个系统时钟周期；

图 6.1 读操作时序 1 (读 AD 值)

图 6.2 读操作时序 2 (除 AD 值之外的寄存器)

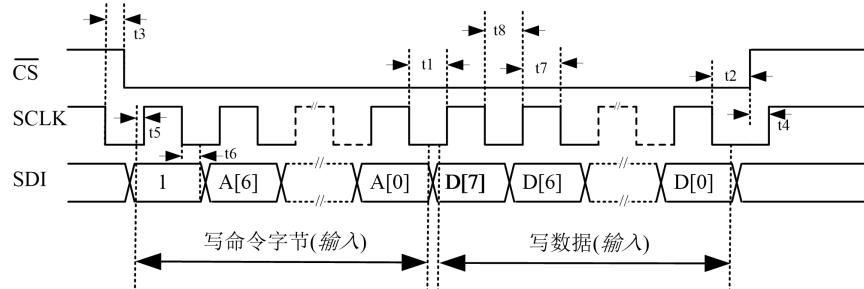

### 6.1.2 写时序

工作过程：

外部设备在CS有效后，先通过SDA写入命令字节，再写入数据字节。注意：

- 1).以字节为单位传输，高比特位在前，低比特位在后；

- 2).多字节寄存器，先传输高字节内容，再传输低字节内容；

- 3).外部设备在SCLK上升沿写数据，CS1253在SCLK下降沿读取数据；

- 4).数据字节之间的时间 t1 要大于等于 2 个系统时钟周期;

- 5).最后一个字节的 LSB 传送完毕,  $\overline{CS}$ 由低变高结束数据传输。SCLK 下降沿和 $\overline{CS}$ 上升沿之间的时间 t2 要大于等于 2 个系统时钟周期。

注意: 有写保护功能的寄存器在写操作之前要先写入写使能命令。

图 6.3 写操作时序

表 6.2 三线串行通讯接口时序表

(VDD=3V, GND=0V, Fosc=5.96MHz, 常温)

| 名称 | 解释                            | Min      | Typ | Max | Unit |

|----|-------------------------------|----------|-----|-----|------|

| t1 | 数据字节之间 SCLK 维持低电平的时间          | 2*sysclk | -   | -   | ns   |

| t2 | 最后一个 SCLK 下降沿与 CS 上升沿之间的时间间隔  | 2*sysclk | -   | -   | ns   |

| t3 | CS 下降沿之前 SCLK 保持为低的时间         | 5        | -   | -   | ns   |

| t4 | CS 上升沿之后 SCLK 保持为低的时间         | 5        | -   | -   | ns   |

| t5 | 在 SCLK 上升沿之前, SDA 上有效数据的建立时间  | 5        | -   | -   | ns   |

| t6 | 在 SCLK 下降沿之后, SDA 上有效数据的保持时间  | sysclk   | -   | -   | ns   |

| t7 | 在 SCLK 上升沿之后, SDO 能稳定输出所需要的时间 | 50       | -   | -   | ns   |

| t8 | SCLK 的高电平宽度                   | 2*sysclk | -   | 170 | us   |

| t9 | SCLK 的低电平宽度                   | 2*sysclk | -   | 680 | us   |

## 7 封装

CS1253 采用 WLCSP16 封装。

图 7.1 WLCSP16 封装尺寸信息

图 7.2 WLCSP16 PCB 封装图